# **TMC2376**

# **PC-to-TV Video Standards Converter**

#### **Features**

- Programmable to VESA and Industry Standard timing modes.

- · Frame rate Conversion

- · Programmable 2D scaling

- Frame-store memory controller

- Accepts 640x480, 800x600, 1024x768 VGA, Mac

- Multiple output standards: NTSC, NTSC-EIA, PAL-B/G/H/I, SCART, Y/C, CVBS, RGB, YUV formats

- · Pan and Zoom

- 3-Line Flicker filter

- I<sup>2</sup>C compatible port controls

- Synclock

- 8-bit A/D converters

- 24-bit RGB input port

- 9-bit output D/A converters

#### **Applications**

- PC video inputs for TVs or interlaced monitors

- TV out for PCs, VGA or graphics cards

- · Internet appliances, net browsers

- · Video Kiosks

See use restrictions on backpage.

## Description

A range of VGA formats/refresh rates can be converted to NTSC and PAL standards compliant with SMPTE-170M and CCIR-624 standards. Within the TMC2376 are capture and encoder engines separated by the frame buffer memory controller. Required external components are minimal: 16M SDRAM memory, clocks and passive parts.

RGB video inputs are converted to the YUV422 format. Vertical scaling and flicker filtering are implemented at the VGA frame rate ahead of the frame store interface.

Frame rate conversion is implemented with by a Frame Store Controller that interfaces with an external SDRAM frame store memory.

YUV422 data is recovered from the memory at the outgoing frame rate. Data is scaled prior to the digital video encoder which generates Y/C and CVBS outputs. For RGB outputs, the encoder may be bypassed via a YUV to RGB transcoder for SCART compatible video.

Setup is via an I<sup>2</sup>C compatible serial port. Power is derived from +3.3V and +5V supplies. Package is a 128-lead Metric Quad Flat Pack (MQFP).

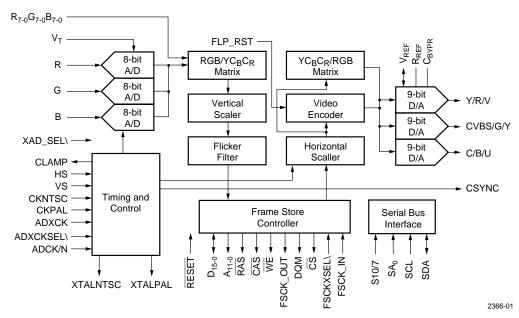

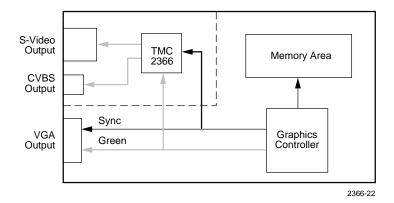

# **Architectural Block Diagram**

Rev. 0.9.4

| Table of Contents                            |    |            |                                             |     |

|----------------------------------------------|----|------------|---------------------------------------------|-----|

| Architectural Overview                       |    | List of Ta | ables and Figures                           |     |

| Video Capture Engine                         | 3  | Table 1.   | Control Register Map                        | 8   |

| Frame Store Memory Controller                |    | Table 2.   | Control Register Power-on Reset States      | 9   |

| Video Encoder Engine                         |    | Table 3.   | NTSC and PAL Frequencies                    |     |

| Serial Control Port                          |    | Table 4.   | NTSC and PAL 4f <sub>SC</sub> Clock Counts  |     |

| Pin Assignments                              |    | Table 5.   | NTSC and PAL Vertical Timing                |     |

| 128-Lead MQFP Package (TMC2376KB)            | 4  | Table 6.   | 4x Clock Connections                        |     |

| Pin Descriptions                             |    | Table 7.   | Serial Port Addresses                       |     |

| Control Register Definitions                 |    | Table 8.   | Supported VESA and Industry                 | 20  |

| Control Register Functions                   |    | Table 6.   | Standard Timing Formats                     | 37  |

| Control Registers Definitions                |    | Table 9.   | Command Register Settings                   |     |

| Functional Description                       |    | Table 10.  | Resolution Categories                       |     |

| Capture Engine                               |    | Table 11.  | Format Subcategories                        |     |

| Timing and Control                           |    |            | NTSC Parameter Register Values, 640x400.    |     |

| Clamps                                       |    |            | PAL Parameter Register Values, 640x400      |     |

| Analog-to-Digital Converters                 |    |            | NTSC Parameter Register Values, 640x480.    |     |

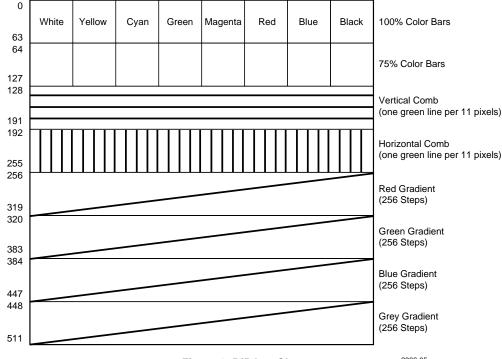

| Internal Bit Pattern Generator               |    |            | PAL Parameter Register Values, 640x480      |     |

| Digital RGB Multiplexer                      | 19 |            | NTSC Parameter Register Values, 800x600.    |     |

| RGB Gain                                     |    |            | PAL Parameter Register Values, 800x600      |     |

| RGB/YUV Matrix                               |    |            | NTSC Parameter Register Values,             |     |

| Vertical Scaler                              |    | 14010 10.  | 1024x768 Resolution                         | 42  |

| Flicker Filter                               |    | Table 19.  | PAL Parameter Register Values,              |     |

| Frame Store Controller                       |    |            | 1024x768 Resolution                         | 43  |

| SDRAM Interface                              |    | Table 20.  | Default BiPGEN Test Pattern Parameters      |     |

| Phase Locked Loop                            |    |            |                                             |     |

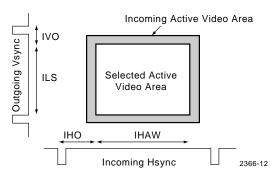

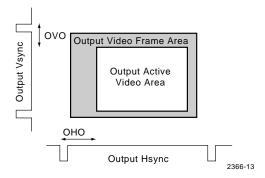

| Input Offset and Size Control                | 22 | Figure 1.  | Functional Block Diagram                    | 17  |

| Output Offset and Size Control               | 22 | Figure 2.  | FAZE Sets ADCK Sampling Edge on             |     |

| Freeze Frame                                 |    | 8          | Incoming Pixels                             | 18  |

| Zoom                                         |    | Figure 3.  | BiPGen Chart                                |     |

| Encoder Engine                               |    | Figure 4.  | Siting of YUV samples determined by         |     |

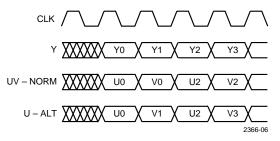

| Outgoing TV Formats                          |    | U          | UVALT                                       | 19  |

| Timing and Control                           | 24 | Figure 5.  | Frame Store Data Bus Format                 |     |

| Horizontal Scaler                            |    | Figure 6.  | SDRAM Mode register setup                   |     |

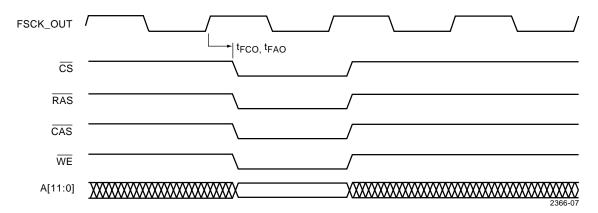

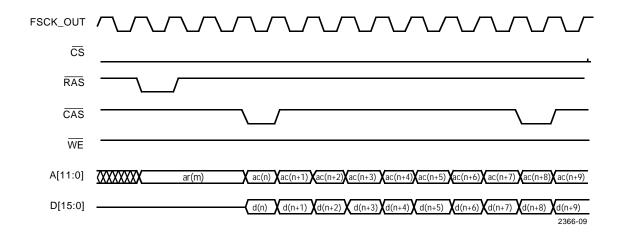

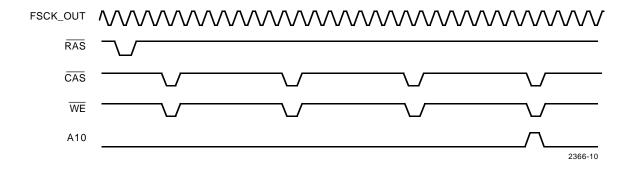

| Digital Video Encoder                        |    | Figure 7.  | Frame Store Mode Register Write Timing      |     |

| YUV/RGB Matrix                               |    | Figure 8.  | Frame Store Data Write Timing               |     |

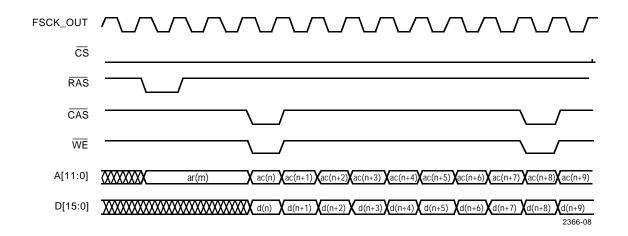

| Digital-to-Analog Converters                 |    | Figure 9.  | Frame Store Data Read Timing                |     |

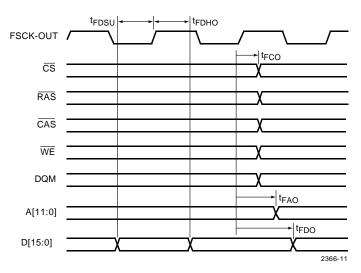

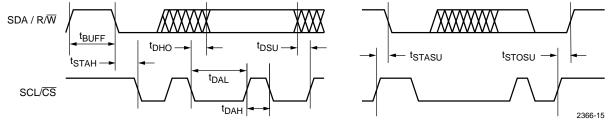

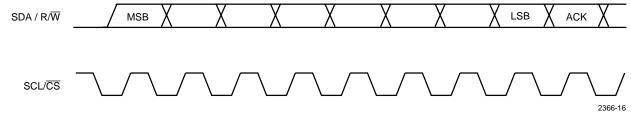

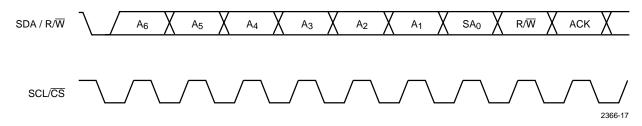

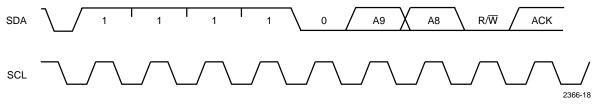

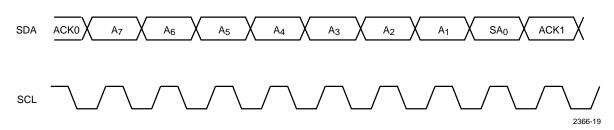

| Serial Control Port (R-Bus)                  |    |            | Frame Store Write Cycle with Auto Precharge |     |

| Data Transfer via Serial Interface           |    |            | Timing Parameter Definition, SDRAM          |     |

| Serial Interface Read/Write Examples         |    |            | Interface                                   | 22  |

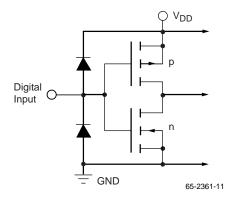

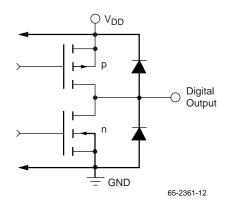

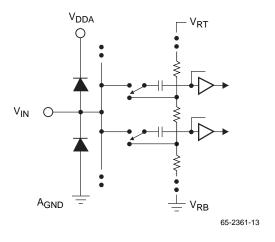

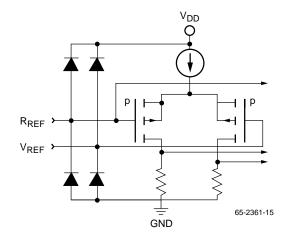

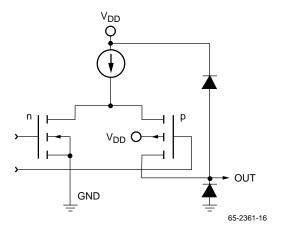

| Equivalent Circuits Absolute Maximum Ratings |    | Figure 12. | Input Offset and Size Definitions           | 22  |

| Operating Conditions                         |    | Figure 13. | Output Horizontal and Vertical Offset       |     |

| Electrical Characteristics                   |    |            | Definitions                                 | 23  |

| Switching Characteristics                    |    |            | Zoomed image showing offsets                |     |

| System Performance Characteristics           |    |            | Serial Port Read/Write Timing               |     |

| Application Notes                            |    |            | Serial Interface – Typical Byte Transfer    |     |

| Circuit Example - PC                         | 33 |            | 7-bit Slave Address with Read/Write Bit     |     |

| Design Example - TV                          | 33 |            | 10-bit address transfer, upper two bits     |     |

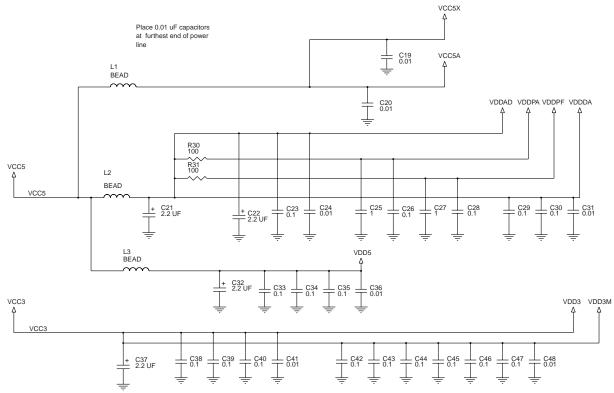

| Power and Ground                             | 35 |            | 10-bit address transfer, lower eight bits   |     |

| Printed Wiring Board Layout                  | 36 |            | Equivalent Digital Input Circuit            |     |

| Video Formats/Register Settings              |    |            | Equivalent Digital Output Circuit           |     |

| Incoming VGA Formats                         |    |            | Equivalent A/D Input Circuit                |     |

| Programming Strategy                         |    |            | Equivalent D/A Reference Input Circuit      |     |

| Programming the Command Registers            |    |            | Equivalent D/A Output Circuit               |     |

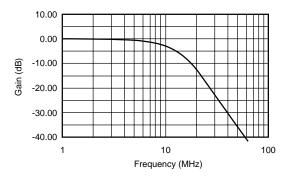

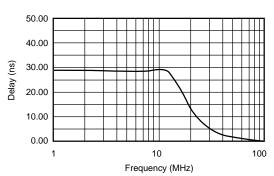

| Zoom Mode                                    |    |            | Video Filter Response                       |     |

| Read Only Registers                          |    |            | Video Filter Delay                          | 33  |

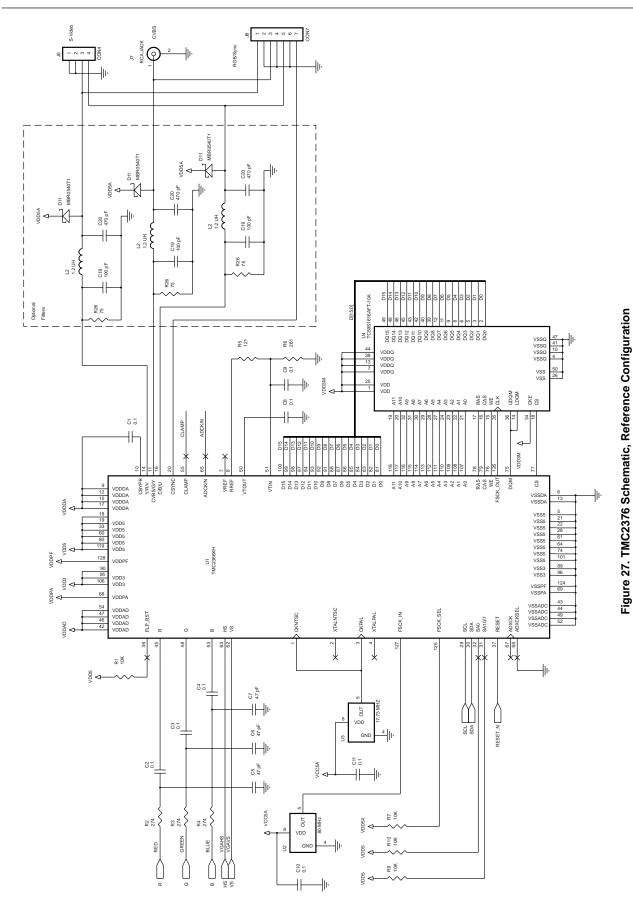

| Programming the Parameter Registers          |    | Figure 27. | TMC2376 Schematic, Reference                |     |

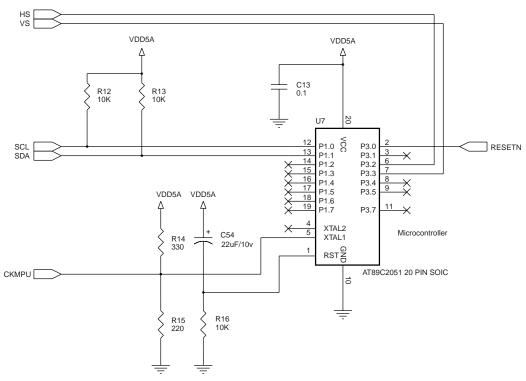

| Decision Tree                                |    |            | Configuration                               |     |

| Parameter Register Values                    |    | Figure 28. | Reference Schematic, Microcontroller        | 35  |

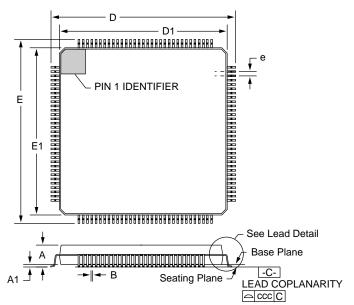

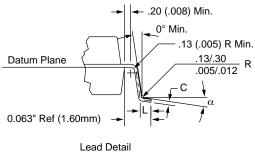

| Mechanical Dimensions                        | 44 |            | Power Distribution Strategy                 | 36  |

| 128-Lead MQFP (KB) Package                   |    | Figure 30. | Layout, Connection and Power                | ~ - |

| Ordering Information                         |    |            | Distribution Strategy                       | 36  |

| =                                            |    |            |                                             |     |

#### **Architectural Overview**

Overall design structure is outlined in this section. Details of how to use and setup the TMC2376 are included in the Functional Description section.

RGB video inputs are asynchronously converted to either NTSC/PAL, YUV or RGB video formats. Architecturally, the TMC2376 is divided into five major sections:

- Video Capture Engine

- · Clock Processor

- Frame Store Controller

- Video Encoder Engine

- · Serial Bus Interface

Besides power and a few external passive components, the TMC2376 requires only a single 16M external SDRAM and external clocks to implement a high quality video standards converter.

Analog RGB inputs with separate horizontal and composite sync signals are accepted. Analog video must be AC coupled to allow clamping during the horizontal sync period. Digital inputs must be 24-bit RGB clocked by external clock, ADXCK.

A wide range of resolution formats can be accepted, including VESA and industry standards such as 640x480, 800x600 and 1024x768. Incoming RGB signals are converted to either the NTSC or PAL TV Standards. Output video format can be selected to be either composite, Y/C, RGB or YUV.

Incoming frame rate can range from 56 to 95 Hz. The Video Capture engine runs asynchronously relative to the Video Encoder Engine. An external frame store memory separates the two engines with write and read access controlled by the TMC2376.

Transformation operations include overscan, underscan, pan and zoom. Scaling operations are separated by the frame store with vertical down-sampling incorporated into the Capture Engine and horizontal up-sampling incorporated into the Encoder Engine.

#### Video Capture Engine

AC coupled RGB video inputs are clamped to ground. Triple 8-bit A/D converters digitize the analog RGB inputs at rates of up to 50 Ms/s. Internal A/D sample clock, ADCK is derived from a phase locked loop referenced to the leading edge of horizontal sync. Either positive or negative sync polarity is accepted.

The selected input (A/D converter outputs or TMC2376 digital RGB) is transcoded by the color matrix into the 16-bit  ${\rm YC_BC_R}422$  format. Next, the Vertical Scaler reduces the number of incoming video lines by the selected scaling factor. Finally, the 3-line Flicker Filter averages lines to eliminate flicker between horizontal lines or along horizontal boundaries.

#### Frame Store Memory Controller

Inserted between the capture and the encoder engines, the frame store has two functions: one is to act as a reservoir of pixels to match the incoming frame rate the outgoing field rate; the other is to support vertical scaling by allowing lines to be written into the frame store intermittently, but read out at a constant rate.

Frame store clock, FS\_CK is derived from the CKNTSC clock by a second phase locked loop that is referenced to the 4 fsc subcarrier clock.

#### Video Encoder Engine

Pixels are retrieved from the external frame store memory asynchronously relative to the incoming frames. Outgoing video timing is set to the selected TV standard, either NTSC or PAL.

Incoming data sampling is normally set to fill complete lines in the Frame Store Memory. Horizontal scaling is applied to pixels exiting the Frame Store. Pixels may be routed through either a digital video encoder or an YCBCR-to-RGB transformation matrix. Either output is connected to a triple 9-bit D/A converter to generate the video output which can be in either CVBS, Y/C, RGB or YUV format.

Encoder Engine timing is derived from one of two 4x subcarrier sources: 14.31818 MHz CKNTSC for NTSC; 17.734475 MHz CKPAL for PAL.

#### **Serial Control Port**

TMC2376 setup is programmed by fourteen 10-bit registers that are accessible via the I<sup>2</sup>C compatible serial port. Status and Revision ID can also be read from the registers.

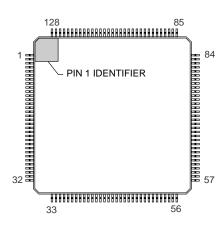

# **Pin Assignments**

## 128-Lead MQFP Package (TMC2376KC)

| Pin | Name     | Pin | Name    | Pin | Name      | Pin | Name     |

|-----|----------|-----|---------|-----|-----------|-----|----------|

| 1   | CKNTSC   | 33  | VDD5X   | 65  | ADCK/N    | 97  | D12      |

| 2   | XTALNTSC | 34  | N/C     | 66  | ADXCKSEL  | 98  | D13      |

| 3   | CKPAL    | 35  | N/C     | 67  | ADXCK     | 99  | D14      |

| 4   | XTALPAL  | 36  | FLP_RST | 68  | VDDPA     | 100 | D15      |

| 5   | VSS5X    | 37  | RESET   | 69  | VSSPA     | 101 | VSS5     |

| 6   | VSSDA    | 38  | R0      | 70  | G3        | 102 | B7       |

| 7   | VREF     | 39  | R1      | 71  | G2        | 103 | B6       |

| 8   | RREF     | 40  | R2      | 72  | G1        | 104 | B5       |

| 9   | VDDDA    | 41  | R3      | 73  | G0        | 105 | B4       |

| 10  | CBPYR    | 42  | VDDAD   | 74  | VSS5      | 106 | VDD3     |

| 11  | CVBS/G/Y | 43  | VSSAD   | 75  | DQM       | 107 | A0       |

| 12  | VDDDA    | 44  | VSSAD   | 76  | WE        | 108 | A1       |

| 13  | VSSDA    | 45  | R       | 77  | <u>cs</u> | 109 | A2       |

| 14  | Y/R/V    | 46  | VDDAD   | 78  | RAS       | 110 | A3       |

| 15  | VDDDA    | 47  | VDDAD   | 79  | CAS       | 111 | A4       |

| 16  | C/B/U    | 48  | G       | 80  | VDD5      | 112 | A5       |

| 17  | VDDDA    | 49  | VSSAD   | 81  | D0        | 113 | A6       |

| 18  | VDD5     | 50  | VTOUT   | 82  | D1        | 114 | A7       |

| 19  | VDD5     | 51  | VTIN    | 83  | D2        | 115 | A8       |

| 20  | CSYNC    | 52  | VSSAD   | 84  | D3        | 116 | A9       |

| 21  | VSS5     | 53  | В       | 85  | D4        | 117 | A10      |

| 22  | VSS5     | 54  | VDDAD   | 86  | D5        | 118 | A11      |

| 23  | XA/D_SEL | 55  | CLAMP   | 87  | D6        | 119 | VDD5     |

| 24  | G4       | 56  | R4      | 88  | D7        | 120 | B3       |

| 25  | G5       | 57  | R5      | 89  | VSS3      | 121 | B2       |

| 26  | G6       | 58  | R6      | 90  | VDD3      | 122 | B1       |

| 27  | G7       | 59  | R7      | 91  | D8        | 123 | B0       |

| 28  | VSS5X    | 60  | VDD5X   | 92  | D9        | 124 | VSSPF    |

| 29  | SCL      | 61  | VSS5X   | 93  | D10       | 125 | FSCKXSEL |

| 30  | SDA      | 62  | VS      | 94  | D11       | 126 | FSCK_OUT |

| 31  | SA10/7   | 63  | HS      | 95  | VDD3      | 127 | FSCK_IN  |

| 32  | SA0      | 64  | VSS5X   | 96  | VSS3      | 128 | VDDPF    |

# **Pin Descriptions**

|               | Pin<br>Number   |                            |                                                                                                                                                                                                                                                                        |

|---------------|-----------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name      | 128-pin<br>MQFP | Type/Value                 | Pin Function Description                                                                                                                                                                                                                                               |

| Clocks        | •               |                            |                                                                                                                                                                                                                                                                        |

| CKNTSC        | 1               | TTL<br>compatible<br>input | Reference Clock Input, NTSC. Input from 14.31818 MHz external oscillator; or one pin of a crystal connected between CKNTSC and XTALNTSC. NTSC subcarrier frequency is derived from this 4x clock. CKNTSC must be connected (see <i>Table 4. 4x Clock Connections</i> ) |

| XTALNTSC      | 2               | TTL output                 | NTSC Crystal Return. If a crystal is used, connect one pin to CKNTSC, the other to XTALNTSC.                                                                                                                                                                           |

| CKPAL         | 3               | TTL compatible input       | Reference Clock, PAL. Input from 17.734475 MHz external oscillator; or one pin of a crystal connected between CKPAL and XTALPAL. PAL subcarrier frequency is derived from this 4x clock.                                                                               |

| XTALPAL       | 4               | TTL output                 | <b>PAL Crystal Return.</b> If a crystal is used, connect one pin to CKPAL, the other to XTALPAL.                                                                                                                                                                       |

| HS            | 63              | TTL input                  | <b>VGA Horizontal Sync Input.</b> Active HIGH or active LOW polarity is sensed.                                                                                                                                                                                        |

| VS            | 62              | TTL input                  | <b>VGA Vertical Sync Input.</b> Active HIGH or active LOW polarity is sensed.                                                                                                                                                                                          |

| Global Contro | ols             |                            |                                                                                                                                                                                                                                                                        |

| FLP_RST       | 36              | TTL input                  | <b>Field, Line and Pixel Reset.</b> Resets video encoder engine to the start location on the outgoing frame. Used for genlock.                                                                                                                                         |

| RESET         | 37              | TTL input                  | <b>Reset.</b> Resets internal state machines and initializes default register values.                                                                                                                                                                                  |

| A/D Converte  | r Interface     |                            |                                                                                                                                                                                                                                                                        |

| R, G, B       | 45, 48, 53      | 700/1000<br>mV pp          | <b>Analog red, blue and green inputs.</b> AC coupled RGB video input signals. Nominal voltage range is 0.7 Volt peak-to-peak. Inputs are clamped to ground when HS_IN is active.                                                                                       |

| VT            | 51              | 750/1050 mV                | <b>A/D Converter Top Reference Voltage Input.</b> Input to voltage follower that supplies current to A/D converter reference resistors. Range is 0.5 - 2.0 volts.                                                                                                      |

| VTOUT         | 50              | 750/1050 mV                | <b>A/D Converter Top Reference Voltage Output.</b> Voltage follower connection to top of A/D converter reference resistors.                                                                                                                                            |

| ADXCK         | 67              | TTL compatible input       | <b>A/D converter clock.</b> Analog-to-digital converter external clock input if ADXCKSEL = H.                                                                                                                                                                          |

| ADXCKSEL\     | 66              | TTL input                  | ADXCK select. Selects the ADCK source:  ADXCKSEL\ = L: external clock applied to the ADXCK pin.  ADXCKSEL\ = H: internal phase-locked loop.                                                                                                                            |

| ADCK/N        | 65              | TTL output                 | <b>ADCK divided by N.</b> ADCK divided by N for connection to external phase-locked loop controller.                                                                                                                                                                   |

| CLAMP         | 55              | TTL output                 | <b>Clamp out.</b> Clamp output signal. CLAMPO = H, when the internal clamp is active during the horizontal sync period, HS_IN.                                                                                                                                         |

# Pin Descriptions (continued)

|                   | Pin<br>Number                                   |              |                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name          | 128-pin<br>MQFP                                 | Type/Value   | Pin Function Description                                                                                                                                                                                                                                                                                              |

| Digital RGB I     | nputs                                           |              |                                                                                                                                                                                                                                                                                                                       |

| R <sub>7-0</sub>  | 59, 58, 57,<br>56, 41, 40,<br>39, 38            | TTL input    | Digital red input. 8-bit red input data.                                                                                                                                                                                                                                                                              |

| G <sub>7-0</sub>  | 27, 26, 25,<br>24, 70, 71,<br>72, 73            | TTL input    | Digital green input. 8-bit green input data.                                                                                                                                                                                                                                                                          |

| B <sub>7-0</sub>  | 102, 103,<br>104, 105,<br>120, 121,<br>122, 123 | TTL input    | Digital blue input. 8-bit blue input data.                                                                                                                                                                                                                                                                            |

| XAD_SEL\          | 23                                              | TTL input    | <b>Digital/analog RGB in select</b> . LOW selects external digital $R_{7-0}G_{7-0}B_{7-0}$ inputs; HIGH selects internal A/D converters with $R_{7-0}G_{7-0}B_{7-0}$ set to active outputs, states undefined.                                                                                                         |

| Video Output      | ts                                              |              |                                                                                                                                                                                                                                                                                                                       |

| Y/R/V             | 14                                              | Analog Video | Video output. As programmed by Command Register DACFMT <sub>1-0</sub> bits:  00 Luminance component Y of S-video  01 Red component of RGB  1X V component of YUV                                                                                                                                                      |

| CVBS/G/Y          | 11                                              | Analog video | Video output. As programmed by Command Register DACFMT <sub>1-0</sub> bits:  00 Composite video.  01 Green component of RGB.  1X Y component of YUV.                                                                                                                                                                  |

| C/B/U             | 16                                              | Analog Video | Video output. As programmed by Command Register DACFMT <sub>1-0</sub> bits:  00 Chrominance component of S-video.  01 Blue component of RGB.  1X U component of YUV.                                                                                                                                                  |

| CSYNC             | 20                                              | TTL output   | <b>Composite sync output.</b> Digital composite sync for YUV and RGB/SCART video outputs.                                                                                                                                                                                                                             |

| Voltage Refe      | rence                                           |              |                                                                                                                                                                                                                                                                                                                       |

| VREF              | 7                                               | +1.235 V     | Voltage reference input/output. If unconnected, except for a $0.1\mu F$ capacitor to ground for noise decoupling, the internal 1.235 Volt band-gap reference will be supplied to the three D/A Converters . An external 1.235 volt reference connected to the VREF pin, will override the internal voltage reference. |

| R <sub>REF</sub>  | 8                                               | 392/768Ω     | <b>Reference resistor.</b> Connected between R <sub>REF</sub> and ground, this resistor sets the current range of the D/A converters Use $392\Omega$ for a $37.5\Omega$ load and $768\Omega$ for a $75\Omega$ load.                                                                                                   |

| C <sub>BYPR</sub> | 10                                              | 0.1 μF       | Bypass Capacitor. A $0.1\mu F$ capacitor must be connected between CBYPR and VDDDA to reduce noise at the D/A outputs.                                                                                                                                                                                                |

# Pin Descriptions (continued)

|                    | Pin<br>Number           |                            |                                                                                                                                                                                                                                  |  |

|--------------------|-------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | 128-pin                 |                            |                                                                                                                                                                                                                                  |  |

| Pin Name           | MQFP                    | Type/Value                 | Pin Function Description                                                                                                                                                                                                         |  |

| Frame Buffer       |                         |                            |                                                                                                                                                                                                                                  |  |

| D <sub>15</sub> -0 | 100-97,<br>94-91, 88-81 | TTL input/<br>output       | <b>Data port, frame store memory.</b> 16-bit data bus for 16M SDRAM.                                                                                                                                                             |  |

| A <sub>11</sub> -0 | 118-107                 | TTL output                 | <b>Address port, frame store memory.</b> 12-bit address bus for 16M SDRAM.                                                                                                                                                       |  |

| RAS                | 78                      | TTL output                 | <b>Row address strobe.</b> RAS output for 16M SDRAM frame store memory.                                                                                                                                                          |  |

| CAS                | 79                      | TTL output                 | <b>Column address strobe.</b> CAS output for 16M SDRAM frame store memory.                                                                                                                                                       |  |

| WE                 | 76                      | TTL output                 | Write enable. WE output for 16M SDRAM frame store memory.                                                                                                                                                                        |  |

| DQM                | 75                      | TTL output                 | <b>Data Qualify.</b> Qualify data for 16M SDRAM frame store read/write operations. State is set by the memory access mode:                                                                                                       |  |

|                    |                         |                            | DQM = L, enables memory outputs for read operations and exposes memory inputs for write operations.                                                                                                                              |  |

|                    |                         |                            | DQM = H, disables memory outputs and masks memory inputs                                                                                                                                                                         |  |

| CS                 | 77                      | TTL output                 | SDRAM chip select. CS output for 16M SDRAM frame store memory.                                                                                                                                                                   |  |

| FSCK_IN            | 127                     | TTL<br>compatible<br>input | Frame store clock input. Clock input to be routed to FSCK_OL selected if FSCK_SEL = L.                                                                                                                                           |  |

| FSCKXSEL\          | 125                     | TTL input                  | Frame store clock select. Selects either internal or external clock for 16M SDRAM frame store memory. If FSCKXSEL\= H, the internal clock synthesized from CKNTSC is selected. With FSCKXSEL\= L, the FSCK_IN input is selected. |  |

| FSCK_OUT           | 126                     | TTL output                 | <b>Frame store clock output</b> . FSCK_OUT for 16M SDRAM frame store memory.                                                                                                                                                     |  |

| Serial Port        |                         |                            |                                                                                                                                                                                                                                  |  |

| SA10/7             | 31                      | TTL input                  | Serial address length select. Selects the length of the serial address:  SA10/7 = L: 10-bits SA10/7 = H: 7-bits                                                                                                                  |  |

| SA <sub>0</sub>    | 32                      | TTL input                  | Serial data address bit 0 Selects the serial bus address SA <sub>0</sub> = L: 0x6A, Ox276 SA <sub>0</sub> = H: 0x4A, Ox224                                                                                                       |  |

| SDA                | 30                      | TTL input                  | Serial data. Data line of the serial port.                                                                                                                                                                                       |  |

| SCL                | 29                      | TTL input                  | Serial clock. Clock line of the serial port.                                                                                                                                                                                     |  |

| Power and G        | round                   |                            |                                                                                                                                                                                                                                  |  |

| VDDAD              | 42, 46, 47, 54          | +5.0 V                     | A/D converter Power.                                                                                                                                                                                                             |  |

| VDDPA              | 68                      | +5.0 V                     | <b>ADCK Phase-locked loop Power</b> . Filtered +5 volt power for ADCK phase locked loop.                                                                                                                                         |  |

| V <sub>DD3</sub>   | 90, 95, 106             | +3.3 V                     | Digital Power. 3.3 volt power for memory interface.                                                                                                                                                                              |  |

## Pin Descriptions (continued)

|                  | Pin<br>Number                        |            |                                                                                                          |

|------------------|--------------------------------------|------------|----------------------------------------------------------------------------------------------------------|

| Pin Name         | 128-pin<br>MQFP                      | Type/Value | Pin Function Description                                                                                 |

| VDDPF            | 128                                  | +5.0 V     | <b>FSCK Phase-locked loop Power.</b> Filtered +5 volt power for FSCK phase locked loop.                  |

| V <sub>DD5</sub> | 18, 19, 33,<br>60, 80, 119           | +5.0 V     | <b>Digital Power.</b> 5 volt power for digital sections of chip excluding the 3.3 volt memory interface. |

| VDDDA            | 9, 12, 15, 17                        | +5.0 V     | D/A Converter Power.                                                                                     |

| VSSAD            | 43, 44, 49, 52                       | 0 V        | A/D Converter Ground.                                                                                    |

| VSSPA            | 69                                   | 0 V        | ADCK phase-locked loop ground.                                                                           |

| VSS3             | 89, 96                               | 0 V        | Digital ground. +3.3 volt power return.                                                                  |

| VSSPF            | 124                                  | 0 V        | FSCK phase-locked loop ground.                                                                           |

| V <sub>SS5</sub> | 5, 21, 22, 28,<br>61, 64, 74,<br>101 | 0 V        | Digital ground. +5 volt power return.                                                                    |

| VSSDA            | 6, 13                                | 0 V        | D/A Converter Ground.                                                                                    |

## **Control Register Definitions**

#### **Control Register Functions**

Control register functions are summarized in Table 1. Capture Engine parameter registers have no prefix; Command and Status registers are prefixed by 1; Encoder parameter registers are prefixed by 2.

Each internal register is 10-bits wide. To access a register two 8-bit data words must be transferred. In the case of a write,

writing the second byte loads the internal 10-bit register. Most registers have type read/write. Read only registers access the internal status of the TMC2376. Write-only registers initiate the transfer of data.

For typical settings, see Video Formats/Register Settings.

**Table 1. Control Register Map**

| Reg.               | Bit #          | Name                                     | Туре |  |  |

|--------------------|----------------|------------------------------------------|------|--|--|

| Input h            | orizontal off  | set                                      |      |  |  |

| 0                  | 7-0            | IHO <sub>7-0</sub>                       | R/W  |  |  |

| 1                  | 1-0            | IHO <sub>9-8</sub>                       | R/W  |  |  |

| Input v            | ertical offset |                                          |      |  |  |

| 2                  | 7-0            | IVO <sub>7-0</sub>                       | R/W  |  |  |

| 3                  | 1-0            | IVO <sub>7-0</sub><br>IVO <sub>9-8</sub> | R/W  |  |  |

| Input h            | orizontal act  | ive width                                |      |  |  |

| 4                  | 7-0            | IHAW <sub>7-0</sub>                      | R/W  |  |  |

| 5                  | 1-0            | IHAW <sub>9-8</sub>                      | R/W  |  |  |

| Input lines stored |                |                                          |      |  |  |

| 6                  | 7-0            | ILS <sub>7-0</sub>                       | R/W  |  |  |

| 7                  | 1-0            | ILS <sub>7-0</sub> ILS <sub>9-8</sub>    | R/W  |  |  |

| Reg.                         | Bit #                               | Name               | Туре |  |  |  |  |  |

|------------------------------|-------------------------------------|--------------------|------|--|--|--|--|--|

| Input h                      | Input horizontal samples (per line) |                    |      |  |  |  |  |  |

| 8                            | 7-0                                 | IHS <sub>7-0</sub> | R/W  |  |  |  |  |  |

| 9                            | 1-0                                 | IHS <sub>9-8</sub> | R/W  |  |  |  |  |  |

| Input horizontal count       |                                     |                    |      |  |  |  |  |  |

| Α                            | 7-0                                 | IHC <sub>7-0</sub> | R    |  |  |  |  |  |

| В                            | 1-0                                 | IHC <sub>9-8</sub> | R    |  |  |  |  |  |

| Input vertical count (lines) |                                     |                    |      |  |  |  |  |  |

| С                            | 7-0                                 | IVC <sub>7-0</sub> | R    |  |  |  |  |  |

| D                            | 1-0                                 | IVC <sub>9-8</sub> | R    |  |  |  |  |  |

| Vertical scaling coefficient |                                     |                    |      |  |  |  |  |  |

| Е                            | 5-0                                 | VSC <sub>5-0</sub> | RW   |  |  |  |  |  |

| F                            | -                                   | -                  | W    |  |  |  |  |  |

Table 1. Control Register Map (continued)

| Reg.    | Bit #        | Name               | Туре |

|---------|--------------|--------------------|------|

| Comma   | and register |                    |      |

| 10      | 7-0          | CR <sub>7-0</sub>  | R/W  |

| 11      | 1-0          | CR <sub>9-8</sub>  | R/W  |

| Status  | port         |                    |      |

| 12      | 3-0          | S <sub>3-0</sub>   | R    |

| 13      | _            |                    | _    |

| Comma   | and register | extended           |      |

| 14      | 7-0          | CRE <sub>7-0</sub> | R/W  |

| 15      | 1-0          | CDE <sub>9-8</sub> | R/W  |

| Not use | ed           |                    |      |

| 16 - 1F |              |                    |      |

| Output horizontal offset      |                                               |     |  |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------|-----|--|--|--|--|--|--|--|

| 7-0                           | ОНО <sub>7-0</sub>                            | R/W |  |  |  |  |  |  |  |

| _                             | _                                             | R/W |  |  |  |  |  |  |  |

| Output vertical offset        |                                               |     |  |  |  |  |  |  |  |

| 7-0                           | OVO <sub>7-0</sub>                            | R/W |  |  |  |  |  |  |  |

| 1-0                           |                                               | R/W |  |  |  |  |  |  |  |

| Horizontal scaling coeficient |                                               |     |  |  |  |  |  |  |  |

| 5-0                           | HSC <sub>7-0</sub>                            | R/W |  |  |  |  |  |  |  |

| _                             | _                                             | R/W |  |  |  |  |  |  |  |

| Not used                      |                                               |     |  |  |  |  |  |  |  |

| _                             | _                                             | _   |  |  |  |  |  |  |  |

|                               | vertical offso<br>7-0<br>1-0<br>tal scaling o |     |  |  |  |  |  |  |  |

Status of internal registers following reset at power-up, is shown in Table 2. Note that all unused bits are set to zero and all unused register bits are set 0 for readback.

**Table 2. Control Register Power-on Reset States**

|       | Name                               | Function                       | Value hex (dec)        |

|-------|------------------------------------|--------------------------------|------------------------|

| 01,00 | IHO <sub>9-0</sub>                 | Input horizontal offset        | 80 (128)               |

| 03,02 | IVO <sub>9-0</sub>                 | Input vertical offset          | 80 (128)               |

| 05,04 | IHAW <sub>9-0</sub>                | Input horizontal active width  | 200 (512)              |

| 07,06 | ILS <sub>9-0</sub>                 | Input lines stored             | DC (220)               |

| 09,08 | IHS <sub>9-0</sub>                 | Input horizontal samples       | 2FE (766)              |

| В,А   | IHC <sub>8-0</sub>                 | Input horizontal count         | 112 (274) <sup>1</sup> |

| D,C   | IVC <sub>9-0</sub>                 | Input vertical count           | 2FE (766) <sup>1</sup> |

| F,E   | VSC <sub>5-0</sub>                 | Vertical scaling coefficient   | 000                    |

| 11,10 | CR <sub>9-0</sub> Command register |                                | 001                    |

| 12    | S <sub>7-0</sub> Status register   |                                | 00 <sup>2</sup>        |

| 13    | — Not used                         |                                | 00                     |

| 15,14 | CRE <sub>9-0</sub>                 | Command register extended      | 004                    |

| 16-1F | _                                  | Not used                       | 00                     |

| 21,20 | OHO <sub>7-0</sub>                 | Output horizontal offset       | 0C0 (192)              |

| 23,22 | IVO <sub>7-0</sub>                 | Output vertical offset         | 020 (32)               |

| 25,24 | HSC <sub>5-0</sub>                 | Horizontal scaling coefficient | 000                    |

| 26-2F | -                                  | Not used                       | 00                     |

- 1. May vary.

- 2. 01 if PLL is locked.

#### **Control Registers Definitions**

In the following definitions, range is defined as:

{min value:[max value]}.

#### Input Horizontal Offset Register Low (0)

| 1HO <sub>7</sub> 1HO <sub>6</sub> 1HO <sub>6</sub> 1HO <sub>4</sub> 1HO <sub>2</sub> 1HO <sub>3</sub> 1HO <sub>1</sub> 1HO <sub>0</sub> | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|                                                                                                                                         | IHO <sub>7</sub> | IH0 <sub>6</sub> | IH0 <sub>5</sub> | IHO <sub>4</sub> | IHO <sub>3</sub> | IHO <sub>2</sub> | IHO <sub>1</sub> | IHO <sub>0</sub> |

#### Input Horizontal Offset Register High (1)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IHO <sub>9</sub> | IHO <sub>8</sub> |

| Reg  | Bit#     | Bit Name           | Description                                                                                                                                                                                                                                  |

|------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

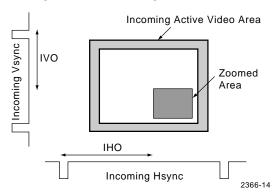

| 1, 0 | 1-0, 7-0 | IHO <sub>9-0</sub> | Input horizontal offset bits [9-0]. Horizontal displacement of the image in pixels from the leading edge of horizontal sync. Programming a value greater than IHS is illegal, preventing any pixels from being written into the Frame Store. |

Range: {0 : [(Input Horizontal Samples(0x8,0x9) + 1) - Input Horizontal Active Width(0x4,0x5)]}.

Due to pipeline delays within the TMC2376, a bias of 42 must be added to the delay from the leading edge of sync to the start of active video expressed in A/D clock sampling ticks. For example, with a 40 MHz sampling clock and a

56.29 kHz line rate, there are 711 samples per line. Typical blanking period is 20% from the leading edge of horizontal sync to the start of active video, leading to a delay of 142 pixels. Adding 42 pixels, the correct OHO value is 184.

#### Input Vertical Offset Low (2)

|     | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|-----|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|     | IVO <sub>7</sub> | IV0 <sub>6</sub> | IV0 <sub>5</sub> | IVO <sub>4</sub> | IV0 <sub>3</sub> | IVO <sub>2</sub> | IVO <sub>1</sub> | IVO <sub>0</sub> |

| Inp | out Vertical C   | Offset High (3)  |                  |                  |                  | _                |                  |                  |

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IVO <sub>9</sub> | IV0 <sub>8</sub> |

| Reg  | Bit#     | Bit Name           | Description                                                                                                                                       |

|------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 2 | 1-0, 7-0 | IVO <sub>9-0</sub> | <b>Input vertical offset bits [9:0].</b> Vertical displacement of the image in lines from the leading edge of vertical sync plus a one line bias. |

Range: {0 : [Input Vertical Count (0xC,0xD) - Input Lines Stored (0x6,0x7)]}.

Constraining the upper limit of the range prevents IVO from forcing the last line of an image with height ILS beyond the range of IVC.

#### Note:

1. Input Vertical Count (0xC,0xD) must be read to obtain the register value.

#### Input Horizontal Active Width Low (4)

| 7                 | 6                 | 5                 | 4                 | 3                 | 2                 | 1                 | 0                 |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| IHAW <sub>7</sub> | IHAW <sub>6</sub> | IHAW <sub>5</sub> | IHAW <sub>4</sub> | IHAW <sub>3</sub> | IHAW <sub>2</sub> | IHAW <sub>1</sub> | ihaw <sub>0</sub> |

#### Input Horizontal Active Width High (5)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                 | 0                 |

|---|---|---|---|---|---|-------------------|-------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IHAW <sub>9</sub> | IHAW <sub>8</sub> |

| Reg  | Bit#     | Bit Name            | Description                                                                                                                                                     |

|------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 4 | 1-0, 7-0 | IHAW <sub>9-0</sub> | Input horizontal active width [9:0]. Number of incoming pixels to be stored in the Frame Store Memory following extraction from the incoming active video area. |

Range: {0 : [{((Input Horizontal Samples (0x8,0x9) + 1) - Incoming Video Horizontal Blank):[720]}]}.

#### Note

1. IHAW optimizes the number of stored pixels. Line store capacity limits the maximum value of IHAW to 720 active pixels per video line.

#### Input Lines Stored Low (6)

| ILS <sub>7</sub> | ILS <sub>7</sub> |

|------------------|------------------|

#### Input Lines Stored High (7)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | ILS <sub>9</sub> | ILS <sub>8</sub> |

| Reg  | Bit#     | Bit Name           | Description                                                                                                                                                        |

|------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | 1-0, 7-0 | ILS <sub>9-0</sub> | Input lines stored bits [9:0]. Number of incoming lines per field to be stored in the Frame Store Memory following extraction from the incoming active video area. |

Range: {0 : [{(Input Vertical Count (0xC,0xD) - Incoming Video Vertical Blank) \* (1 - (Input Line Drop Coefficient (0xE,0xF)/64))/ 2:[PAL or NTSC Active lines per field]}].

- 1. Input number of lines accepted = ILS \* 2 \* [64 / (64 VSC)].

- 2. VSC is the vertical scaling coefficient. The term in [] brackets is the reciprocal of the vertical scaling factor. A factor of two is included to account for interlace.

#### Input Horizontal Samples Low (8)

| 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| IHS <sub>7</sub> | IHS <sub>6</sub> | IHS <sub>5</sub> | IHS <sub>4</sub> | IHS <sub>3</sub> | IHS <sub>2</sub> | IHS <sub>1</sub> | IHS <sub>0</sub> |

#### Input Horizontal Samples High (9)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IHS <sub>9</sub> | IHS <sub>8</sub> |

| Reg  | Bit#     | Name               | Description                                                                                                                                                                                                 |

|------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 8 | 1-0, 7-0 | IHS <sub>9-0</sub> | Input horizontal line samples bits [9:0]. Terminal count of the number of clocks per horizontal line between incoming horizontal sync pulses. Internal ADCK phaselocked loop is programmed with this value. |

$\label{eq:Range: Range: ADCK PLL Frequency * Input Horizontal Count (0xA,0xB) *(NTSC 4f_{SC} Period - ( PAL_NTSC ( 0x10,0x11:Bit 1) * (NTSC 4f_{SC} Period - PAL 4f_{SC} Period))):[\{Max ADCK PLL Frequency * Input Horizontal Count (0xA,0xB) * (NTSC 4f_{SC} Period - (PAL_NTSC (0x10,0x11:Bit 1) * (NTSC 4f_{SC} Period - PAL 4f_{SC} Period))):[1022]\}]\}.$

#### Note:

1. ADCK PLL frequency = 4f<sub>SC</sub> \* IHS / IHC. Accounting for the maximum and minimum PLL VCO frequencies establishes the limits on the range of IHS. In the range equation, the PAL\_NTSC bit controls addition of the difference between NTSC and PAL 4f<sub>SC</sub> clock periods.

#### Input Horizontal Count Low (A)

| 7                | 6                               | 5                | 4                | 3                | 2                | 1                | 0                |  |  |  |  |

|------------------|---------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|

| IHC <sub>7</sub> | IHC <sub>6</sub>                | IHC <sub>5</sub> | IHC <sub>4</sub> | IHC <sub>3</sub> | IHC <sub>2</sub> | IHC <sub>1</sub> | IHC <sub>0</sub> |  |  |  |  |

| Input Horizont   | Input Horizontal Count High (R) |                  |                  |                  |                  |                  |                  |  |  |  |  |

#### input Horizontal Count High (B)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                |

|---|---|---|---|---|---|---|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | IHC <sub>8</sub> |

| Reg  | Bit#   | Bit Name           | Description                                                                                                                                                                                                                                                                                                                        |

|------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B, A | 0, 7-0 | IHC <sub>8-0</sub> | Input horizontal count bits [8:0] (read only). Number of 4f <sub>SC</sub> clock pulses per horizontal line. 4f <sub>SC</sub> is the selected 4X subcarrier clock (17.734 MHz for PAL or 14.318 MHz for NTSC). IHC can be read to determine the incoming horizontal line frequency for auto selection of the incoming video format. |

Range: {0:[511]}.

0

TMC2376 PRODUCT SPECIFICATION

#### Input Vertical Count Low (C)

| 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| IVC <sub>7</sub> | IVC <sub>6</sub> | IVC <sub>5</sub> | IVC <sub>4</sub> | IVC <sub>3</sub> | IVC <sub>2</sub> | IVC <sub>1</sub> | IVC <sub>0</sub> |

#### Input Vertical Count High (D)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IVC <sub>9</sub> | IVC <sub>8</sub> |

| Reg  | Bit#     | Bit Name           | Description                                                                                                                                                                                                                   |

|------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D, C | 1-0, 7-0 | IVC <sub>9-0</sub> | Input vertical line count bits [9:0] (read only). Terminal count of the number of incoming lines per frame. IVC is used to determine the incoming vertical refresh frequency for auto selection of the incoming video format. |

Range: {0:[1022]}.

0

#### **Vertical Scaling Coefficient (E)**

0

0

| 7                                | 6 | 5                | 4                | 3                | 2                | 1                | 0                |  |

|----------------------------------|---|------------------|------------------|------------------|------------------|------------------|------------------|--|

| 0                                | 0 | VSC <sub>5</sub> | VSC <sub>4</sub> | VSC <sub>3</sub> | VSC <sub>2</sub> | VSC <sub>1</sub> | vsc <sub>0</sub> |  |

| Vertical Scaling Coefficient (F) |   |                  |                  |                  |                  |                  |                  |  |

| 7                                | 6 | 5                | 4                | 3                | 2                | 1                | 0                |  |

0

0

| Reg | Bit# | Bit Name           | Description                                                                                                                                                                                                                   |

|-----|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E   | 5-0  | VSC <sub>5-0</sub> | Vertical scaling coefficient bits [5:0], m. The number of lines that must be removed modulo 64 to down-sample the incoming frame to the number of active lines in the outgoing TV frame. Vertical scaling factor = (1 - m/64) |

lines that must be removed modulo 64 to down-sample the incoming frame to the number of active lines in the outgoing TV frame. Vertical scaling factor = (1 - m/64).

F - Load . Writing to register F activates register E data.

Range: {0:[{(1 - (2 \* Input Lines Stored(Offset 0x6,0x7) /(Input Vertical Count(Offset 0xC,0xD) - Input Vertical Blank))) \* 64:[32]}]}.

In the above range, the vertical scaling coefficient, n is limited by the constraint that the scaling factor cannot reduce the number of input lines below the number of lines programmed to be stored. For example, 500 input lines cannot be scaled by 1/2 if the number of stored lines programmed is 300. However, if the number of stored lines, ILS is lowered to 200, then 200 of the 250 lines will be stored although the last 50 will be discarded.

**Example:** 480 line VGA image mapped to 400 line image.

0

0

VSC = (1-(400/480))\*64 = 10.6667

Use 11 for the Coefficient value.

## Command Register Low (10)

| 7    | 6       | 5     | 4   | 3       | 2    | 1        | 0     |

|------|---------|-------|-----|---------|------|----------|-------|

| CBPF | LUMNTCH | UVALT | FRZ | RGBGAIN | ZOOM | PAL/NTSC | RESET |

## Command Register High(11)

| 7 | 6 | 5 | 4 | 3 | 2 | 1                   | 0                   |

|---|---|---|---|---|---|---------------------|---------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | DACFMT <sub>1</sub> | DACFMT <sub>0</sub> |

| Reg | Bit# | Bit Name              | Description                                                                  |

|-----|------|-----------------------|------------------------------------------------------------------------------|

| 11  | 1-0  | DACFMT <sub>1-0</sub> | DAC Output Format. Selects between: 0 0 Y/C and CVBS 0 1 RGB 1 0 YUV 1 1 YUV |

| 10  | 7    | CBPF                  | Bypass chroma bandpass filter     Insert chroma bandpass filter              |

| 10  | 6    | LUMNTCH               | Bypass luminance notch filter     Insert luminance notch filter              |

| 10  | 5    | UVALT                 | Cosite U and V samples     Alternate U and V samples                         |

| 10  | 4    | FRZ                   | Continuous update     Freeze frame                                           |

| 10  | 3    | RGBGAIN               | 0: 1X input gain 1: 1.43 input gain                                          |

| 10  | 2    | ZOOM                  | 0: Zoom off<br>1: Zoom on                                                    |

| 10  | 1    | PAL/NTSC              | select NTSC video output timing     select PAL video output timing           |

| 10  | 0    | RESET                 | 0: reset video pipeline (control registers are not affected)     1: run      |

## Status Register (12)

| 7                  | 6                  | 5                  | 4                  | 3       | 2 | 1 | 0        |

|--------------------|--------------------|--------------------|--------------------|---------|---|---|----------|

| REVID <sub>3</sub> | REVID <sub>2</sub> | REVID <sub>1</sub> | revid <sub>0</sub> | STRTERR | 0 | 0 | PLL_LOCK |

| Reg | Bit# | Bit Name | Description                                                                                                                                                                  |

|-----|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | 7-4  | REVID    | Chip revision identification. Starts at 0                                                                                                                                    |

| 12  | 3    | STRTERR  | Output Video Start Position. Flag indicates if active video has been programmed to overlay output horizontal sync.  0: Start position within limits  1: Start position error |

| 12  | 2-1  | -        | Not used                                                                                                                                                                     |

| 12  | 0    | PLL_LOCK | SCLK PLL status. 0: unlocked 1: locked                                                                                                                                       |

#### **Unused Register (13)**

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Note:

1. Register 13 is the unused mate of register 12. 00 hex will be read back from register 13.

#### **Command Register Extended Low (14)**

| 7           | 6              | 5         | 4       | 3      | 2      | 1   | 0      |

|-------------|----------------|-----------|---------|--------|--------|-----|--------|

| FAZE        | _              | YCOFF     | COMPOFF | ADCOFF | BIPGEN | OCS | FLIKON |

| Command Don | istor Extended | Himb (45) |         |        |        |     |        |

#### Command Register Extended High (15)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reg | Bit# | Bit Name | Description                                                                                                                                                                                                                             |  |  |  |

|-----|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14  | 7    | FAZE     | Sample phase. Sets the phase of the RGB A/D converter sampling clock.  H = normal.  L = inverted                                                                                                                                        |  |  |  |

| 14  | 6    | -        | Reserved                                                                                                                                                                                                                                |  |  |  |

| 14  | 5    | YCOFF    | Luma and chroma video D/A converter power.  0 = Power on  1 = Power off                                                                                                                                                                 |  |  |  |

| 14  | 4    | COMPOFF  | Composite video D/A Converter Power.  0 = Power on  1 = Power off                                                                                                                                                                       |  |  |  |

| 14  | 3    | ADCOFF   | Analog-to-digital Converter Power.  0 = Power on  1 = Power off                                                                                                                                                                         |  |  |  |

| 14  | 2    | BIPGEN   | Built In Test Pattern Generator. 0: Select video input 1: Select test pattern                                                                                                                                                           |  |  |  |

| 14  | 1    | ocs      | Output Chroma Scale. Sets the gain of the chrominance channel for optional de-saturation of colors.  0: 1X (normal)  1: 0.75X (de-saturate)                                                                                             |  |  |  |

| 14  | 0    | FLICKON  | Flicker Filter On. Disables flicker filter to enhance vertical definition. Or enables three line vertical filtering to reduce line-to-line flicker on interlaced images.  0: bypass vertical filter.  1: three line vertical filtering. |  |  |  |

| Reg | Bit# | Bit Name | Description |

|-----|------|----------|-------------|

| 15  | 1    | -        | Reserved.   |

| 15  | 0    | -        | Reserved.   |

#### **Output Horizontal Offset Low (20)**

| 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 0H0 <sub>7</sub> | 0H0 <sub>6</sub> | 0H0 <sub>5</sub> | 0H0 <sub>4</sub> | 0H0 <sub>3</sub> | 0H0 <sub>2</sub> | 0H0 <sub>1</sub> | оно <sub>0</sub> |

#### Output Horizontal Offset High (21)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reg | Bit# | Bit Name           | Description                                                                                                                                                  |  |

|-----|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20  | 7-0  | ОНО <sub>7-0</sub> | Output horizontal offset [7:0]. Horizontal displacement of the outgoing active video area image in pixels from the leading edge of outgoing horizontal sync. |  |

| 21  | -    | -                  | Load. Writing to register 21 activates register 20 data.                                                                                                     |  |

Range: { HBlank for NTSC or PAL in pixels:[255]}.

#### **Output Vertical Offset Low (22)**

|                                  | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|----------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|                                  | 0V0 <sub>7</sub> | 0V0 <sub>6</sub> | 0V0 <sub>5</sub> | 0V0 <sub>4</sub> | 0V0 <sub>3</sub> | 0V0 <sub>2</sub> | 0V0 <sub>1</sub> | ovo <sub>0</sub> |

| Output Vertical Offset High (23) |                  |                  |                  |                  |                  |                  |                  |                  |

| = |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reg | Bit# | Bit Name           | Description                                                                                                                                                                              |

|-----|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22  | 7-0  | OVO <sub>7-0</sub> | Output vertical offset [7:0]. Vertical displacement of the outgoing active video area in lines from the beginning of the equalization pulses: line 1/263 for NTSC; line 311/623 for PAL. |

| 23  | _    | _                  | Load. Writing to register 23 activates register 22 data.                                                                                                                                 |

Range: {VBlank for NTSC or PAL in lines:[255]}.

#### **Horizontal scaling Coefficient (24)**

| ſ | 7 |   | E                | 1                | 2                | 2                | 1                | 0                |

|---|---|---|------------------|------------------|------------------|------------------|------------------|------------------|

| ı |   | 0 | o o              | 4                | 3                |                  | •                | U                |

|   | _ | _ | HSC <sub>5</sub> | HSC <sub>4</sub> | HSC <sub>3</sub> | HSC <sub>2</sub> | HSC <sub>1</sub> | HSC <sub>0</sub> |

#### **Horizontal scaling Coefficient (25)**

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| _ | _ | _ | _ | _ | _ | _ | _ |

| Reg | Bit# | Bit Name           | Description                                                                                                                                                                                        |

|-----|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | 5-0  | HSC <sub>5-0</sub> | <b>Horizontal scaling coefficient, n [5:0].</b> The number of pixels that must be added modulo 64 to up-sample the outgoing field from the frame store. Horizontal scaling factor = $(1 + n/64)$ . |

| 25  | -    | -                  | Load . Writing to register 25 activates register 24 data.                                                                                                                                          |

Range: {0:[63]}.

**Example:** HSC = 1F hex; n = 31; Scaling factor = (1 + 31/64) = 1.48.

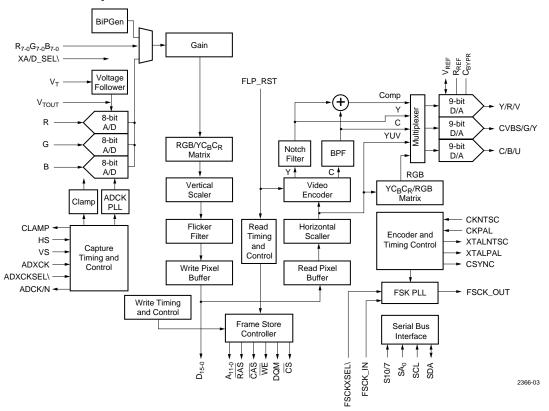

## **Functional Description**

Figure 1. Functional Block Diagram

Details of how to connect and setup the TMC2376 are included in this section. Overall design principles are in the Architectural Overview section. Operation of the TMC2376 is divided into four sections:

- · Capture Engine

- Frame Store Controller

- Encoder Engine

- · Serial Control Port

#### **Capture Engine**

A/D Converters, Bit Pattern Generator, RGB/YUV Matrix, Vertical Scaler and Flicker Filter comprise the Capture Engine.

#### **Timing and Control**

Timing of the Capture Engine is derived from the Input Control Block which contains a series of counters and decoders synchronized to the A/D sample clock, ADCK. ADCK is derived from a phase locked loop referenced to the leading edge of horizontal sync.

Sync polarity is auto-detected by sensing the leading edge of horizontal sync HS and vertical sync, VS. This edge is the reference for the phase-locked loop tracking the horizontal pixel count and the vertical line counter.

Registers that interface with the Capture Timing and Control block are:

- IHS

- IHC (read only)

- IVC (read only)

Capture Control also coordinates hand off of data to the Frame Store Controller.